FIPMS148

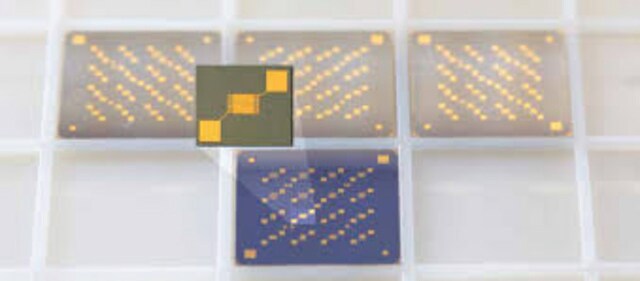

Back-gated OFET Interdigitated Substrate

Au source/drain, 230 nm SiO2 gate-insulator, varied W/L from 500 to 4000, 16 transistors per chip, chips (diced)

About This Item

Produtos recomendados

forma

chips (diced)

chips (each 15 x 15 mm2)

embalagem

pack of 1 (wafer of 60 diced chips)

temperatura de armazenamento

15-25°C

Procurando produtos similares? Visita Guia de comparação de produtos

Descrição geral

Layer structure:

- Gate: n-doped silicon (doping at wafer surface: n~3x1017/ cm3)

- Gate oxide: 230 nm ± 10 nm SiO2 (thermal oxidation)

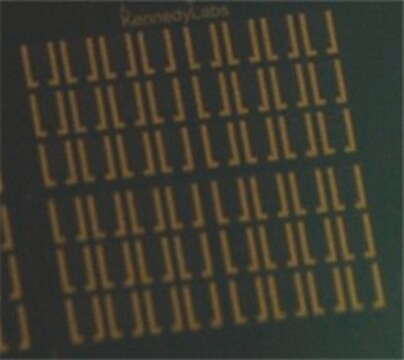

- Drain/source: 30 nm Au with 10 nm high work function adhesion layer (ITO), by lift-off technique

- Protection: resist AR PC 5000/3.1 (soluble in AZ-Thinner or acetone)

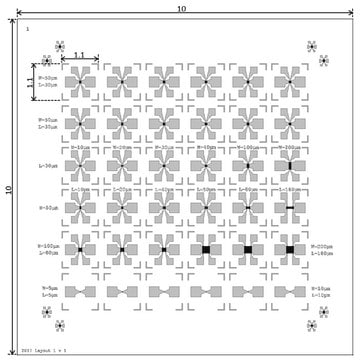

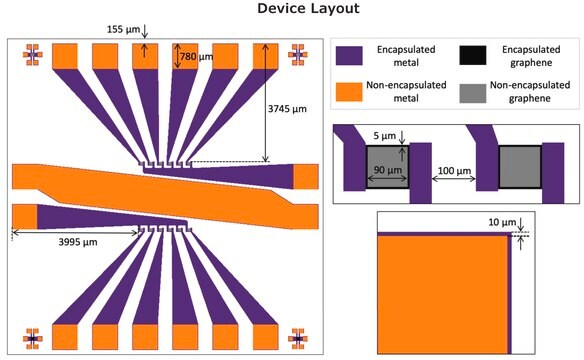

- Layout: see images

- Test chip size: 15 x 15 mm2

- No. of chips: 60 per wafer

- Contact pads: 0.5 x 0.5 mm2

- No. of transistors: 16 per chip

4 x transistors L= 2.5 μm W= 10 mm

4 x transistors L= 5 μm W= 10 mm

4 x transistors L= 10 μm W= 10 mm

4 x transistors L= 20 μm W= 10 mm

Aplicação

Embalagem

Nota de preparo

To guarantee a complete cleaning of the wafer / chip surface from resist residuals, please rinse by acetone and then dry the material immediately by nitrogen (compressed air).

Recommendation for material characterization:

If gate currents appear during the characterization of the field effect transistors, considerable variations could occur at the extraction of the carrier mobility. Therefore it is necessary to check the leakage currents over the reverse side (over the chip edges) of the OFET-substrates.

Armazenamento e estabilidade

Resist layer was applied to prevent damage from scratches.

Expiration date is the recommended period for resist removal only. After resist removal, the substrate remains functional and does not expire.

Informações legais

Certificados de análise (COA)

Busque Certificados de análise (COA) digitando o Número do Lote do produto. Os números de lote e remessa podem ser encontrados no rótulo de um produto após a palavra “Lot” ou “Batch”.

Já possui este produto?

Encontre a documentação dos produtos que você adquiriu recentemente na biblioteca de documentos.

Artigos

Professors Tokito and Takeda share design principles and optimization protocols for organic electronic devices, focusing on flexibility and low cost.

Nossa equipe de cientistas tem experiência em todas as áreas de pesquisa, incluindo Life Sciences, ciência de materiais, síntese química, cromatografia, química analítica e muitas outras.

Entre em contato com a assistência técnica